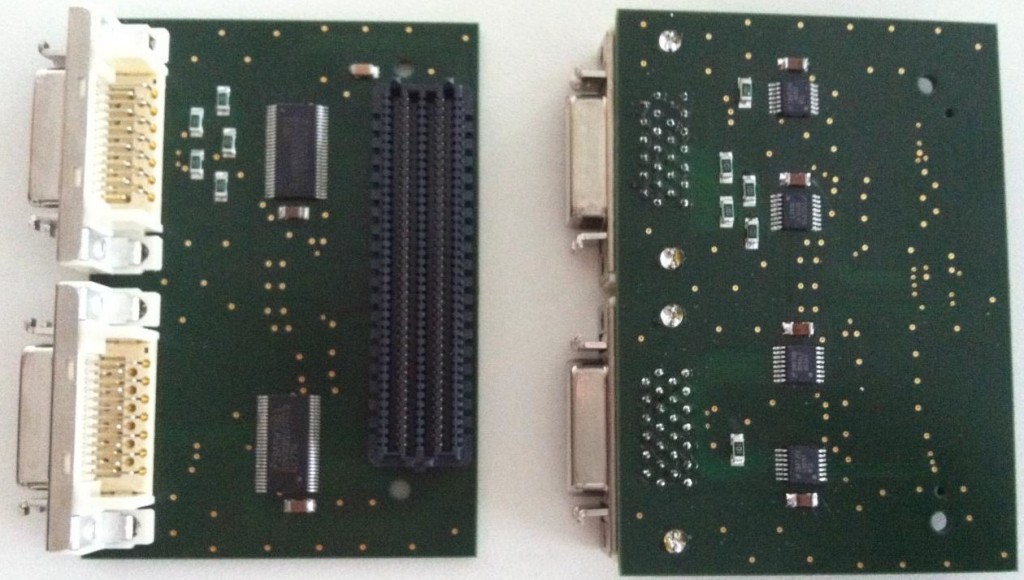

For machine vision applications we need to connect industrial cameras to the zedboard. These cameras often use Camera Link interfaces. Therefore we develop a FMC Module (LPC) with a Camera Link interface for the zedboard. Currently only the base configuration is supported. The second Camera Link connector on the board is a pusher for camera simulation and used for testing.

We tested the image data receiver successfully at clock rate of 85 MHz with the pusher output and with a AViiVA® SC2 CL Color linescan camera. The camera control signals work correctly, too.

We tested the image data receiver successfully at clock rate of 85 MHz with the pusher output and with a AViiVA® SC2 CL Color linescan camera. The camera control signals work correctly, too.

The serial interface of Camera Link was only tested with a input output test. A timing test and the full integration into the operating system will follow in October.

Most of the development were done by students in there student research projects. Substantial contribution came from Nils Lindenthal (left) and Sascha Karmann (right).

Their documentations give detailed information about the hardware, firmware and software. The final work was done by Nils Lindenthal. Documentations are only available in German.

Karmann, S.: Link to document

Lindenthal, N.: Link to document

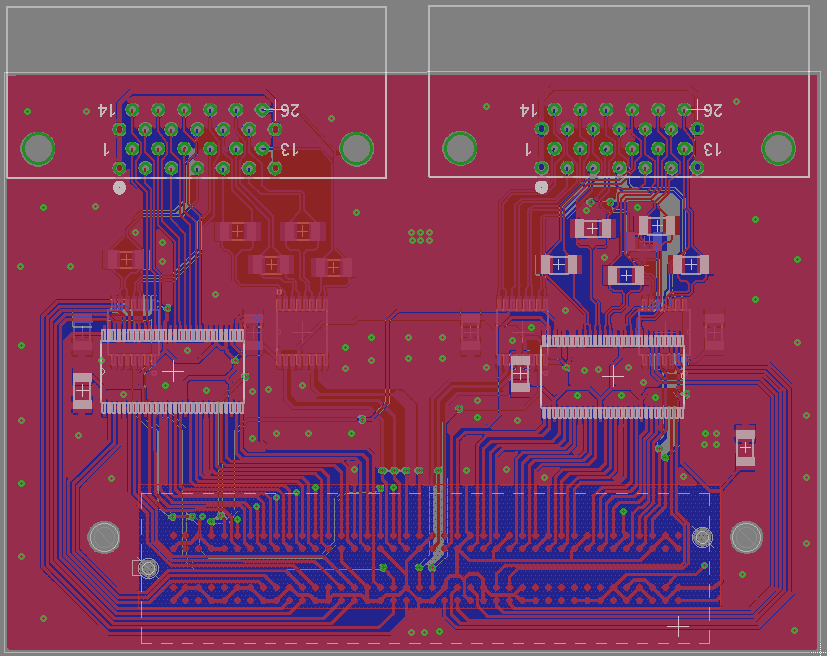

The layout was designed with CadSoft EAGLE PCB.

All source files can be downloaded from https://github.com/roy77/Cameralink-LPC-FMC-Module.